publications

2025

-

Leveraging Hardware Power through Optimal Pulse Profiling for Each Qubit PairYuchen Zhu, Jinglei Cheng, Boxi Li, and 3 more authorsIn 2025 52nd International Symposium on Computer Architecture (ISCA), 2025

Leveraging Hardware Power through Optimal Pulse Profiling for Each Qubit PairYuchen Zhu, Jinglei Cheng, Boxi Li, and 3 more authorsIn 2025 52nd International Symposium on Computer Architecture (ISCA), 2025In the scaling development of quantum computers, the calibration process emerges as a critical challenge. Existing calibration methods, utilizing the same pulse waveform for two-qubit gates across the device, overlook hardware differences among physical qubits and lack efficient parallel calibration. In this paper, we enlarge the pulse candidates for two-qubit gates to three pulse waveforms, and introduce a fine-grained calibration protocol. In the calibration protocol, three policies are proposed to profile each qubit pair with its optimal pulse waveform. Afterwards, calibration subgraphs are introduced to enable parallel calibraton through identifying compatible calibration operations. The protocol is validated on real machine with up to 127 qubits. Real-machine experiments demonstrates a minimum gate error of 0.001 with a median error of 0.006 which is 1.84x reduction compared to default pulse waveform provided by IBM. On device level, a double fold increase in quantum volume as well as 2.3x reduction in error per layered gate are achieved. The proposed protocol leverages the potential current hardware and could server as an important step toward fault-tolerant quantum computing.

@inproceedings{zhu2024leveraginghardwarepoweroptimal, title = {Leveraging Hardware Power through Optimal Pulse Profiling for Each Qubit Pair}, author = {Zhu, Yuchen and Cheng, Jinglei and Li, Boxi and Zhou, Yidong and Ding, Yufei and Liang, Zhiding}, booktitle = {2025 52nd International Symposium on Computer Architecture (ISCA)}, year = {2025}, eprint = {2411.19308}, archiveprefix = {arXiv}, primaryclass = {quant-ph}, url = {https://arxiv.org/abs/2411.19308}, } -

CaliScalpel: In-Situ and Fine-Grained Qubit Calibration Integrated with Surface Code Quantum Error CorrectionXiang Fang, Keyi Yin, Yuchen Zhu, and 8 more authorsIn 2025 52nd International Symposium on Computer Architecture (ISCA), 2025

CaliScalpel: In-Situ and Fine-Grained Qubit Calibration Integrated with Surface Code Quantum Error CorrectionXiang Fang, Keyi Yin, Yuchen Zhu, and 8 more authorsIn 2025 52nd International Symposium on Computer Architecture (ISCA), 2025Quantum Error Correction (QEC) is a cornerstone of fault-tolerant, large-scale quantum computing. However, qubit error drift significantly degrades QEC performance over time, necessitating periodic calibration. Traditional calibration methods disrupt quantum states, requiring system downtime and making in situ calibration infeasible. We present CaliScalpel, an innovative framework for in situ calibration in surface codes. The core idea behind CaliScalpel is leveraging code deformation to isolate qubits undergoing calibration from logical patches. This allows calibration to proceed concurrently with computation, while code enlargement maintains error correction capabilities with minimal qubit overhead. Additionally, CaliScalpel incorporates optimized calibration schedules derived from detailed device characterization, effectively minimizing physical error rates. Our results show that CaliScalpel achieves concurrent calibration and computation with modest qubit overhead and negligible execution time impact, marking a significant step toward practical in situ calibration in surface-code-based quantum computing systems.

@inproceedings{fang2024caliscalpelinsitufinegrainedqubit, title = {CaliScalpel: In-Situ and Fine-Grained Qubit Calibration Integrated with Surface Code Quantum Error Correction}, author = {Fang, Xiang and Yin, Keyi and Zhu, Yuchen and Ruan, Jixuan and Tullsen, Dean and Liang, Zhiding and Sornborger, Andrew and Li, Ang and Humble, Travis and Ding, Yufei and Shi, Yunong}, booktitle = {2025 52nd International Symposium on Computer Architecture (ISCA)}, year = {2025}, eprint = {2412.02036}, archiveprefix = {arXiv}, primaryclass = {quant-ph}, url = {https://arxiv.org/abs/2412.02036}, } -

EPOC: A Novel Pulse Generation Framework Incorporating Advanced Synthesis Techniques for Quantum CircuitsJinglei Cheng, Yuchen Zhu, Yidong Zhou, and 3 more authorsIn 2025 62nd ACM/IEEE Design Automation Conference (DAC), 2025

EPOC: A Novel Pulse Generation Framework Incorporating Advanced Synthesis Techniques for Quantum CircuitsJinglei Cheng, Yuchen Zhu, Yidong Zhou, and 3 more authorsIn 2025 62nd ACM/IEEE Design Automation Conference (DAC), 2025In this paper we propose EPOC, an efficient pulse generation framework for quantum circuits that combines ZX-Calculus, circuit partitioning, and circuit synthesis to accelerate pulse generation. Unlike previous works that focus on generating pulses from unitary matrices without exploring equivalent representations, EPOC employs a finer granularity approach by grouping quantum gates and decomposing the resulting unitary matrices into smaller ones using synthesis techniques. This enables increased parallelism and decreased latency in quantum pulses. EPOC also continuously optimizes the circuit by identifying equivalent representations, leading to further reductions in circuit latency while minimizing the computational overhead associated with quantum optimal control. We introduce circuit synthesis into the workflow of quantum optimal control for the first time and achieve a 31.74% reduction in latency compared to previous work and a 76.80% reduction compared to the gate-based method for creating pulses. The approach demonstrates the potential for significant performance improvements in quantum circuits while minimizing computational overhead.

@inproceedings{cheng2024epoc, title = {EPOC: A Novel Pulse Generation Framework Incorporating Advanced Synthesis Techniques for Quantum Circuits}, author = {Cheng, Jinglei and Zhu, Yuchen and Zhou, Yidong and Ren, Hang and Song, Zhixin and Liang, Zhiding}, booktitle = {2025 62nd ACM/IEEE Design Automation Conference (DAC)}, journal = {arXiv preprint arXiv:2405.03804}, year = {2025}, } -

EDDQC: Enhanced Dynamical Distributing Quantum CompilationYidong Zhou, Kecheng Liu, Haochen Luo, and 6 more authorsIEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2025

EDDQC: Enhanced Dynamical Distributing Quantum CompilationYidong Zhou, Kecheng Liu, Haochen Luo, and 6 more authorsIEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2025This article presents enhanced dynamical distributing quantum compilation (EDDQC), an optimized method for distributed quantum computing (DQC) using linear nearest neighbor (LNN) architecture integrated with quantum switches. By leveraging the symmetry of LNN topology and designating dangling qubits as communication links, our approach optimizes compilation for high local connectivity, sparse full connectivity algorithms (HLC-SFC) like quantum approximate optimization algorithm (QAOA) and quantum Fourier transform (QFT). Experimental results demonstrate significant performance improvements over traditional methods, including reductions in cross-group swaps by up to 67.2%, gate count by 43.8%, and total execution cycles by up to 40%. We also utilize the area law of entanglement entropy to limit entanglement growth in our 1-D system. Our comprehensive approach combines LNN chains’ efficiency with reconfigurable network flexibility, enhancing scalability and robustness for large-scale quantum computations.

@article{11143393, author = {Zhou, Yidong and Liu, Kecheng and Luo, Haochen and Xiong, Lingjun and Zhu, Yuchen and Casey, Eilis and Cheng, Jinglei and Yen-Chi Chen, Samuel and Liang, Zhiding}, journal = {IEEE Transactions on Very Large Scale Integration (VLSI) Systems}, title = {EDDQC: Enhanced Dynamical Distributing Quantum Compilation}, year = {2025}, volume = {}, number = {}, pages = {1-11}, keywords = {Qubit;Quantum computing;Topology;Logic gates;Teleportation;Computer architecture;Quantum entanglement;Entropy;Program processors;Scalability;Dangling qubit;distributed quantum computing (DQC);linear compiler;linear nearest neighbor (LNN);quantum switch}, } -

Autonomous Aerosol and Plasma Co-Jet Printing of Metallic Devices at Ambient TemperatureYipu Du, Jinyu Yang, Kaidong Song, and 5 more authorsSmall, 2025

Autonomous Aerosol and Plasma Co-Jet Printing of Metallic Devices at Ambient TemperatureYipu Du, Jinyu Yang, Kaidong Song, and 5 more authorsSmall, 2025Abstract Additive manufacturing of metallic materials holds the potential to revolutionize the fabrication of functional devices unattainable via traditional methods. Despite recent advancements, printing metallic materials typically requires thermal processing at elevated temperatures to form dense structures with desired properties, which presents a major challenge for direct printing and integration with temperature-sensitive materials. Herein, a unique co-jet printing (CJP) method is reported integrating an aerosol jet and a non-thermal, atmospheric pressure plasma jet to enable concurrent aerosol deposition of metal nanoparticle inks and in situ sintering at ambient temperature. A machine learning algorithm is integrated with the CJP to perform real-time defect detection and autonomous correction, enhancing the yield of printed films with high electrical conductivity from 44% to 94%. Concurrent printing and sintering eliminate the need for post-printing processing, reducing the overall manufacturing time by multiple folds depending on product size. CJP enables direct printing of functional devices on a variety of temperature-sensitive materials including biological materials. Direct printing of hydration sensors on living plant leaves is demonstrated for long-duration monitoring of hydration level in the plant. The versatile CJP method opens tremendous opportunities to harmoniously integrate abiotic and biotic materials for emerging applications in wearable/implantable devices and biohybrid systems.

@article{https://doi.org/10.1002/smll.202409751, author = {Du, Yipu and Yang, Jinyu and Song, Kaidong and Jiang, Qiang and Bappy, Md Omarsany and Zhu, Yuchen and Go, David B. and Zhang, Yanliang}, title = {Autonomous Aerosol and Plasma Co-Jet Printing of Metallic Devices at Ambient Temperature}, journal = {Small}, volume = {21}, number = {11}, pages = {2409751}, keywords = {aerosol and plasma co-jet printing, ambient temperature processing, machine learning optimization, metal nanoparticles}, url = {https://onlinelibrary.wiley.com/doi/abs/10.1002/smll.202409751}, eprint = {https://onlinelibrary.wiley.com/doi/pdf/10.1002/smll.202409751}, year = {2025}, }

2024

-

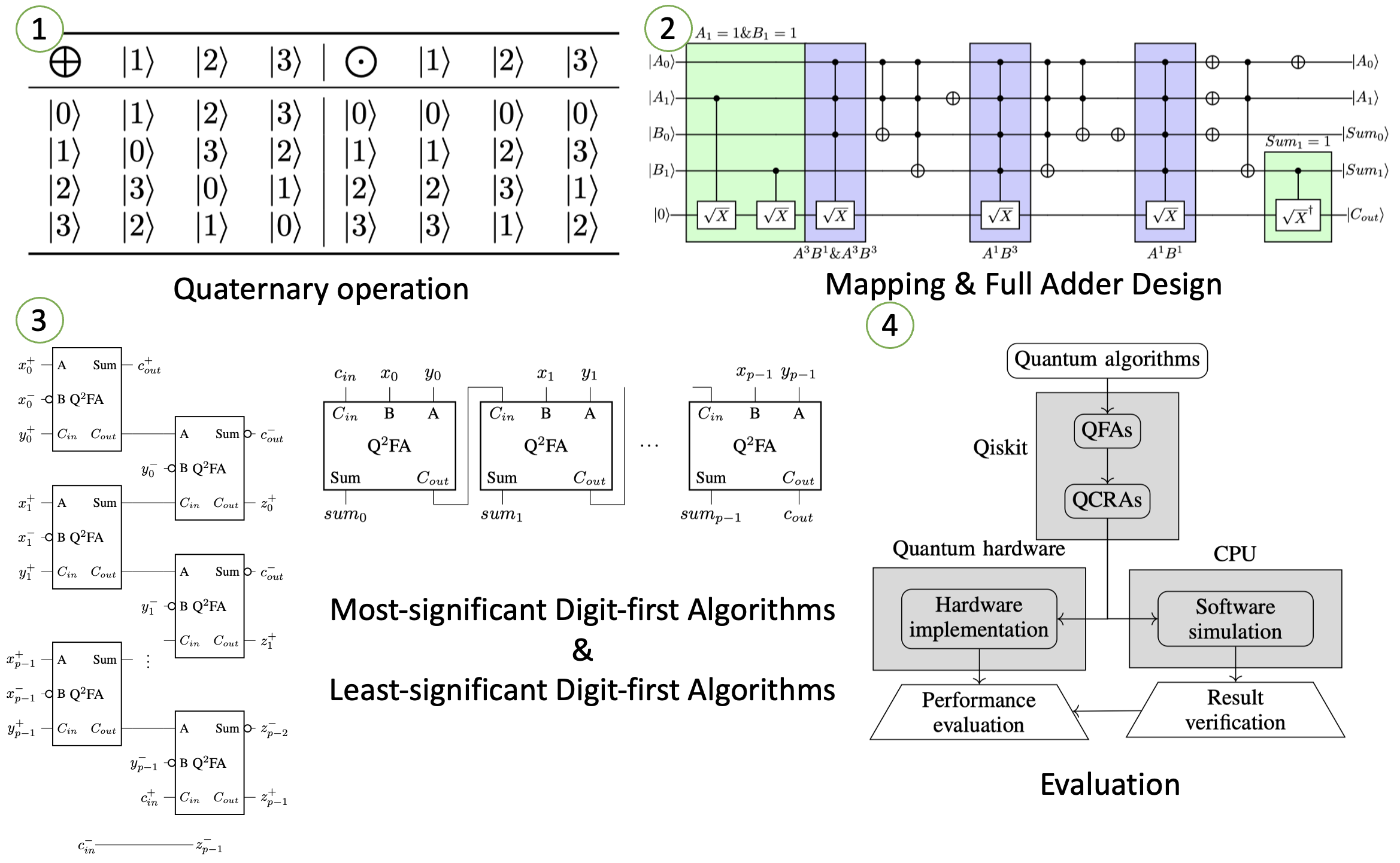

Towards Fault-tolerant Design of Quaternary Quantum ArithmeticYunchen Zhu, Ruixuan Yang, Yuhang Gu, and 3 more authorsIn 2024 IEEE International Test Conference in Asia (ITC-Asia), 2024

Towards Fault-tolerant Design of Quaternary Quantum ArithmeticYunchen Zhu, Ruixuan Yang, Yuhang Gu, and 3 more authorsIn 2024 IEEE International Test Conference in Asia (ITC-Asia), 2024Qudit has emerged as a promising system for next-generation quantum computers because of its significant advantages in multi-phase problems and quantum error correction, while multi-qudit operations are yet to be implemented. As one of the basic operations, quantum addition has been widely applied in number factorization and discrete logarithms. Meanwhile, the physical constraints of noisy intermediate-scale quantum (NISQ) devices necessitate the development of fault-tolerant quantum adders and the exploration of quaternary operations on binary devices is still in its infancy. In this work, we propose the first approach for implementing quaternary quantum addition algorithms by employing primitive quantum gates. A library of quaternary quantum gates and quaternary quantum full adders (\(Q^2FA\)) able to produce carry-first results, along with lower depth and fewer T-gates optimizations are proposed and evaluated, where all circuits are implemented on IBM Qiskit SDK. Extensive experiments show that our proposed \(Q^2FA\) design, together with the optimization techniques, reduces T-depth by up to 1.4\(\times\) and T-count by 1.7\(\times\) compared with baseline quantum circuits without depth and T-gate optimizations. Meanwhile, the scalability of the proposed Q^2FA is demonstrated by constructing quantum carry-ripple adders. Under noisy conditions, our proposed design can achieve an overall fidelity increase by 1.4\(\times\).

@inproceedings{10661353, author = {Zhu, Yunchen and Yang, Ruixuan and Gu, Yuhang and Gu, Fangtian and Kong, Lingyi and Li, He}, booktitle = {2024 IEEE International Test Conference in Asia (ITC-Asia)}, title = {Towards Fault-tolerant Design of Quaternary Quantum Arithmetic}, year = {2024}, volume = {}, number = {}, pages = {1-6}, keywords = {Fault tolerance;Scalability;Qubit;Fault tolerant systems;Logic gates;Noise measurement;Quantum circuit;Quaternary addition;quantum circuits;fault-tolerant design}, doi = {10.1109/ITC-Asia62534.2024.10661353}, } -

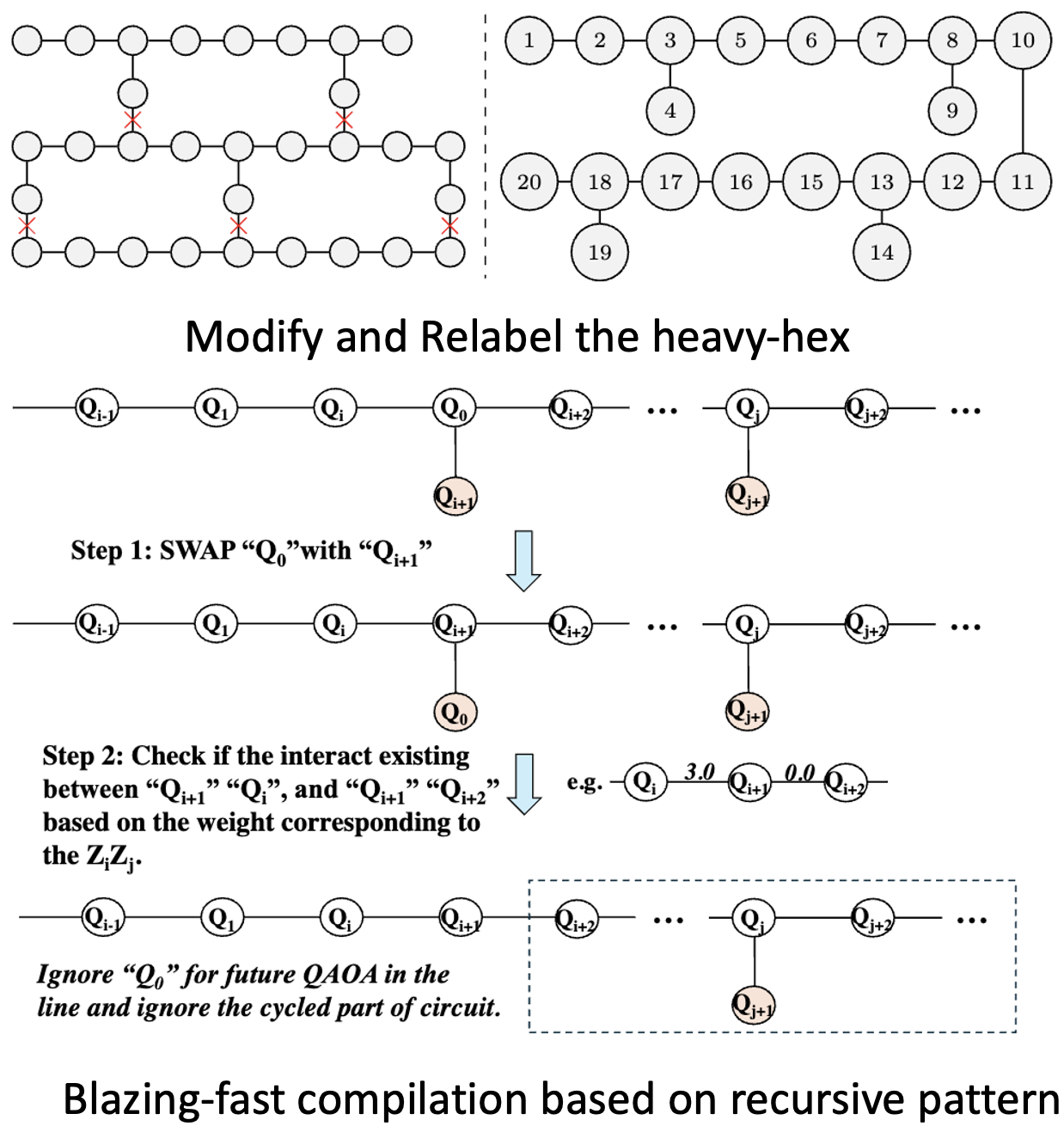

Coqa: Blazing Fast Compiler Optimizations for QAOAYuchen Zhu, Yidong Zhou, Jinglei Cheng, and 4 more authorsIn 2024 IEEE/ACM International Conference on Computer Aided Design (ICCAD), 2024

Coqa: Blazing Fast Compiler Optimizations for QAOAYuchen Zhu, Yidong Zhou, Jinglei Cheng, and 4 more authorsIn 2024 IEEE/ACM International Conference on Computer Aided Design (ICCAD), 2024The Quantum Approximate Optimization Algorithm (QAOA) is one of the most promising candidates for achieving quantum advantage over classical computers. However, existing compilers lack specialized methods for optimizing QAOA circuits. There are circuit patterns inside the QAOA circuits, and current quantum hardware has specific qubit connectivity topologies. Therefore, we propose Coqa to optimize QAOA circuit compilation tailored to different types of quantum hardware. Our method integrates a linear nearest-neighbor (LNN) topology and efficiently map the patterns of QAOA circuits to the LNN topology by heuristically checking the interaction based on the weight of problem Hamiltonian. This approach allows us to reduce the number of SWAP gates during compilation, which directly impacts the circuit depth and overall fidelity of the quantum computation. By leveraging the inherent patterns in QAOA circuits, our approach achieves more efficient compilation compared to general-purpose compilers. With our proposed method, we are able to achieve an average of 30% reduction in gate count and a 39x acceleration in compilation time across our benchmarks.

@inproceedings{zhu2024coqa, title = {Coqa: Blazing Fast Compiler Optimizations for QAOA}, author = {Zhu, Yuchen and Zhou, Yidong and Cheng, Jinglei and Jin, Yuwei and Li, Boxi and Niu, Siyuan and Liang, Zhiding}, booktitle = {2024 IEEE/ACM International Conference on Computer Aided Design (ICCAD)}, journal = {arXiv preprint arXiv:2408.08365}, year = {2024}, volume = {}, number = {}, }